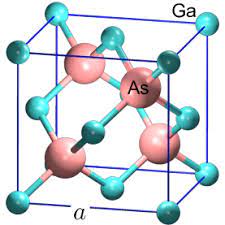

Salah satu metode untuk mengimplementasikan desain suatu sistem mikroelektronika adalah pada suatu keping (chip) silikon. Biasanya luas keping silikon tersebut kurang dari satu sentimeter persegi. Rangkaian elektronika yang ditumbuhkan pada suatu subsrat silikon ataupun gallium arsenide disebut rangkaian terintegrasi atau IC (integrated circuits).

Istilah VLSI (very large scale integration) merujuk pada IC yang memuat 100.000 sampai 10 juta komponen pada subtrat yang sama. Pada dasarnya ada dua macam teknologi rangkaian terintegrasi yang menggunakan silikon sebagai subtrat, yaitu teknologi bipolar dan teknologi MOS (metal oxide semiconductor). Pada teknologi bipolar komponen dasarnya adalah transistor bipolar, sedangkan pada teknologi MOS komponen dasarnya adalah transistor MOS. Teknologi MOS terdiri dari teknologi NMOS, yang menggunakan transistor MOS kanal-N sebagai komponen dasarnya dan teknologi CMOS (Complementary Metal Oxide Semiconductor) dengan transistor MOS kanal-N dan transistor MOS kanal-P sebagai komponen dasarnya. Beberapa tahun belakangan ini teknologi CMOS memegang peranan utama dalam dunia rangkaian terintegrasi. Hal ini disebabkan beberapa keunggulan komparatif di bidang disipasi daya, margin noise, densitas per kemasan, dan kemampuan untuk mengimplementasikan fungsi yang besar dan rumit dengan yield yang tinggi.

Dengan teknologi proses tertentu, pada keping silikon telah dapat ditumbuhkan tidak kurang dari satu juta komponen. DRAM 1M yang dibuat Texas Instruments, yang terdiri dari kira-kira 1 juta transistor dan satu juta kapasitor untuk array memory serta 52.000 transistor untuk unit kontrol, diimplementasikan pada cip seluas 0,54 cm2 dengan menggunakan proses satu mikron. Mikroprosesor Motorola 68020 yang terdiri dari 200.000 transistor dibuat pada cip seluas 0,85 cm2 dengan menggunakan teknologi proses 1,8 mikron.

ADVERTISEMENT

SCROLL TO RESUME CONTENT

Tahapan perancangan

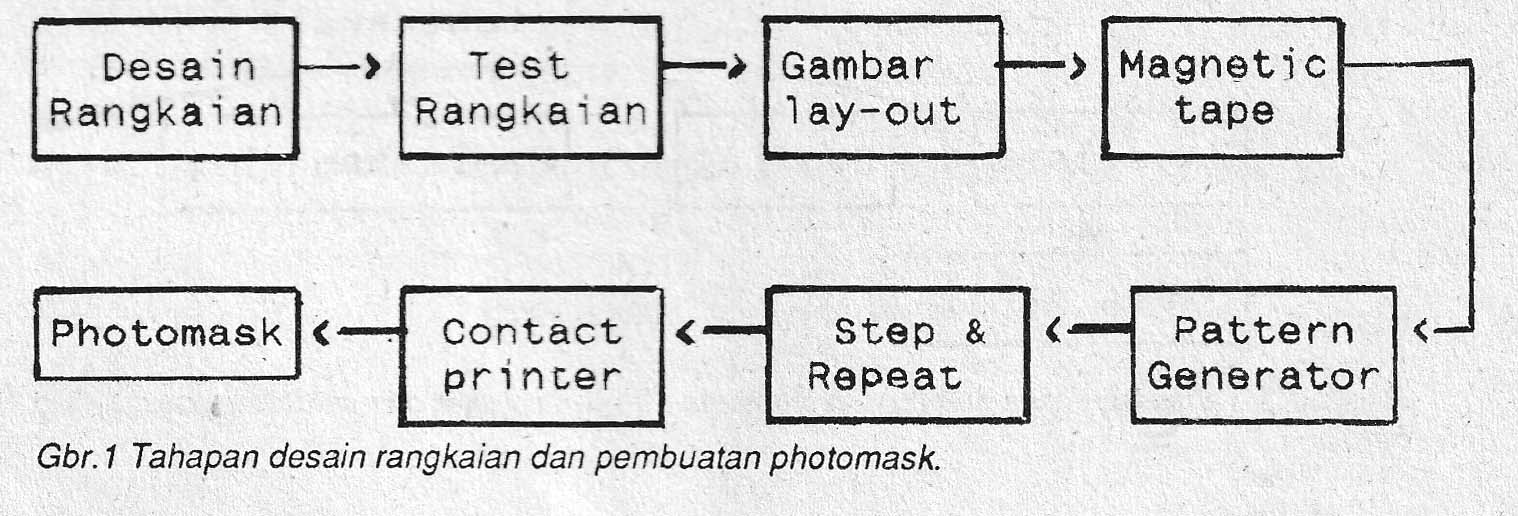

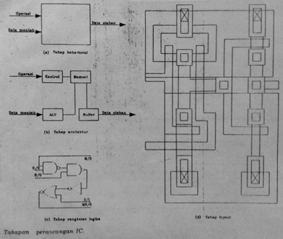

Pada perancangan VLSI IC, beberapa tahap desain harus dilalui. Dari spesifikasi sistem yang dikehendaki dibuat suatu sketsa awal yang merupakan karakteristik perilaku (behavioral) dari sistem tersebut. Karakteristik perilaku ini menggambarkan output sebagai fungsi dari input: saluran mana untuk input dan saluran mana untuk output serta bagaimana hubungan antara input dan output. Tahap ini biasanya juga disebut sebagai tahap black box.

Tahap selanjutnya adalah desain arsitektur dari sistem tersebut. Pada tahap arsitektur, unit-unit fungsional yang membangun sistem, serta interaksi antar unit-unit tersebut didefinisikan. Pada tahap selanjutnya setiap unit fungsional dirancang lebih rinci tetapi masih dalam tingkat abstraksi, biasanya dalam bentuk skematik rangkaian logika.

Tahap terakhir adalah mengkonversikan spesifikasi skematik tersebut menjadi layout IC pada suatu jenis teknologi semikonduktor. Layout IC pada umumnya terbentuk dari poligon-poligon (umumnya segi empat) yang merupakan representasi dari masker-masker yang diperlukan untuk fabrikasi IC tersebut.

Pokok permasalahan

Karena jumlah transistor per cip meningkat pesat maka jumlah rangkaian yang dapat diimplementasikan pada satu cip juga meningkat. Sistem rumit yang dulunya disusun dengan menggunakan banyak cip, sekarang dapat dibuat pada satu atau beberapa cip saja. Hal ini meningkatkan tingkat kerumitan rangkaian dalam satu cip.

Problem yang harus ditanggulangi oleh satu cip menjadi sangat rumit. Sebagai ilustrasi, CPU tradisional seperti pada IBM 360/370 atau pada DEC 11/780 terdiri dari beberapa board rangkaian yang berisi IC-IC SSI (small scale integration) dan MSI (medium scale integration). CPU 32bit yang sedang trendy saat ini (SPARC MIPS dan sebagainya) diimplementasikan pada satu Cip VLSI IC. Mengelola tingkat kerumitan adalah salah satu dari pokok persoalan di dalam desain VLSI IC.

Pokok persoalan kedua adalah waktu yang dibutuhkan untuk merealisasikan satu cip dengan tingkat kerumitan yang tinggi, misalnya mikroprosesor, waktu yang dibutuhkan untuk proses perancangan VLSI dari konsep sampai realisasinya akan meningkat tanpa batas bila tidak digunakan metoda perancangan yang tepat. Sebagai contoh, perancangan suatu mikroprosesor 32 bit membutuhkan lebih dari 20 man-years. Jika desain ini dilakukan oleh satu orang maka asumsi-asumsi yang digunakan pada tahap awal desain kemungkinan besar tidak valid karena teknologi fabrikasi berkembang sangat pesat pada selang-20 tahun tersebut.

Pokok persoalan kedua adalah waktu yang dibutuhkan untuk merealisasikan satu cip dengan tingkat kerumitan yang tinggi, misalnya mikroprosesor, waktu yang dibutuhkan untuk proses perancangan VLSI dari konsep sampai realisasinya akan meningkat tanpa batas bila tidak digunakan metoda perancangan yang tepat. Sebagai contoh, perancangan suatu mikroprosesor 32 bit membutuhkan lebih dari 20 man-years. Jika desain ini dilakukan oleh satu orang maka asumsi-asumsi yang digunakan pada tahap awal desain kemungkinan besar tidak valid karena teknologi fabrikasi berkembang sangat pesat pada selang-20 tahun tersebut.

Suatu solusi yang diajukan haruslah diperiksa kebenaran dan ketepatannya. Meningkatnya tingkat kerumitan suatu sistem berarti meningkatnya kemungkinan gagal-kerja dari sistem tersebut. Dengan demikian verifikasi haruslah dilakukan pada setiap tahap perancangan, agar diperoleh sistem yang bekerja sesuai dengan spesifikasi perancangan. Verifikasi merupakan pokok persoalan yang ketiga.

Pokok persoalan yang keempat yang harus dihadapi adalah mencari solusi yang optimal. Problem yang rumit seperti perancangan VLSI biasanya punya beberapa solusi. Solusi-solusi yang berbeda menjawab aspek-aspek problem dengan tingkat keberhasilan yang berbeda. Tak ada solusi yang sempurna. Lagipula banyak faktor yang mempengaruhi karakteristik hasil perancangan. Dengan demikian pada proses perancangan perlu dilakukan kompromi dengan memprioritaskan unjuk kerja hasil perancangan.

Metodologi perancangan

Tujuan utama setiap perancang IC adalah merancang IC yang memenuhi spesifikasi dalam waktu yang sesingkatnya dan dengan jam kerja yang sesedikit mungkin. Karakteristik lain yang dikehendaki adalah tingkat keberhasilan yang tinggi pada proses fabrikasi, luas cip yang kecil, dan proses fabrikasi yang sederhana.

Selayang tampak bahwa produktivitas perancang akan turun dengan meningkatnya tingkat kerumitan rangkaian. Tapi pada dasarnya hal tersebut tidak perlu terjadi mengingat kebanyakan rangkaian VLSI mempunyai bentuk yang terstruktur. Dengan kata, Iain rangkaian yang rumit tersebut dapat disusun dari rangkaian-rangkaian dasar yang sederhana. Dengan demikian penggunaan metodologi yang tepat dan alat bantu rancangan berkemampuan tinggi dapat menanggulangi masalah menurunnya produktivitas perancang akibat naiknya tingkat kerumitan rangkaian.

Suatu konsep yang amat penting pada semua metodologi perancangan VLSI adalah penjenjangan (hierarchy). Struktur yang berjenjang, terbagi atas tingkat-tingkat. Tingkat-tingkat tersebut dibentuk untuk mengisolasi aktivitas di suatu tingkat terhadap aktivitas di tingkat lain. Isolasi tersebut diperlukan untuk memudahkan pengambilan keputusan, dengan mengeliminasi haI-hal yang ditimbulkan oleh tingkat lainnya.

Penjenjangan terbukti amat bermanfaat pada perancangan rangkaian yang rumit. Konsep mengisolasi bagian-bagian permasalahan menjadi tingkat-tingkat membuat problema keseluruhan yang rumit dapat dipecah menjadi satu himpunan permasalahan yang sederhana. Tiap-tiap permasalahan ini dapat dikerjakan secara terpisah dan dapat dipecah lagi menjadi permasalahan yang lebih sederhana. Proses ini diulang sampai ke tingkat yang paling sederhana. Tiap tingkat disusun atas satu atau beberapa satuan-bentuk (entity). Pada struktu; be}; jenjang’ satuan-bentuk pada suatu tingkat disusun dari beberapa satuan-bentuk dari tingkat yang lebih rendah.

Pada dasarnya ada dua jenis metodologi perancangan VLSI IC, yaitu metoda bottom up dan metoda top-down. Pada metoda bottom up awal perancangan adalah pada tingkat transistor dan tingkat gerbang logika dan kemudian dilanjutkan ke tingkat berikutnya sampai ke tingkat paling atas. Pada metode top-down, perancang berulangkali memecah spesifikasi pada tingkat sistem menjadi kelompok tugas yang sederhana. Contoh penggunaan paling ekstrim dari metoda ini adalah pada Silicon compiler, di mana seluruh blok dirancang otomatis oleh komputer.

Pola perancangan IC digital biasanya menggunakan metode Mead-Conway. Pola desain tersebut bertumpu pada adanya struktur berjenjang serta penggunaan metoda top-down. Menurut metodologi ini suatu sistem digital yang akan diimplementasikan pada cip silikon terbentuk dari sel majemuk (composition cell) dan sel dasar(leafcell). Leafcell terbentuk dari komponen dan kawat penghubung tapi tidak mangandung sel-sel lain. Leafcell berada pada jenjang paling rendah pada struktur hirarki suatu desain. Sel majemuk terdiri dari sel-seL jenjang di bawahnya dan interkoneksi antara sel-sel tersebut. Sel majemuk dapat menempati jenjang mana pun (kecuali jenjang paling bawah) pada struktur hirarki suatu desain.

Harapan

Pada tahun 1979, Carver Mead dan Lynn Conway telah membuka mata dunia bahwa perancangan IC yang sebelumnya hanya dapat dilakukan oleh pabrik-pabrik besar seperti Texas Instruments, Motorola dan lain-lain, dapat dilakukan oleh siapa pun yang berminat mempelajari dan menekuni bidang ini. Metodologi yang dikembangkan oleh Mead-Conway serta keberadaan alat-bantu rancang (computer-aided design) memungkinkan kita untuk mengimplementasikan desain kita sendiri pada cip silikon.

Banyak yang menyatakan bahwa industri semikonduktor berperan setara depgan industri baja pada masa jayanya, dan ada dua proses pada industri semikonduktor yang memberikan nilai-tambah yang besar yaitu proses untuk mendapatkan silikon dengan kemurnian yang sangat tinggi dari pasir kwarsa, dan proses perancangan sistem yang diimplementasikan dalam bentuk lC. Beberapa Institusi di Indonesia PAU Mikroelektronika ITB, LEN-BPlS, INTI-BPIS, LEN-LIPI, KlM-LIPI, PAU Ilmu Komputer UI) sedang melakukan persiapan kearah kegiatan perancangan IC yang professional. Dengan demikian imbauan pionir VLSI di Indonesia Prof Samaun Samadikun, yang mengajak kita untuk menjadi arsitek cip (Swasembada, Oktober 1987) perlu kita renungkan dan kita tanggapi secara positif. Marilah belajar merancang IC.

Achmad Fuad Masud, pengajar pada Jurusan Teknik Elektro ITB dan design engineer pada PAU Mikroelektronika 1TB.

Sumber: Kompas, KAMIS, 28 FEBRUARI 1991